Rekord: SRAM mit extrem niedrigem Energiebedarf

13. Juni 2017

über

über

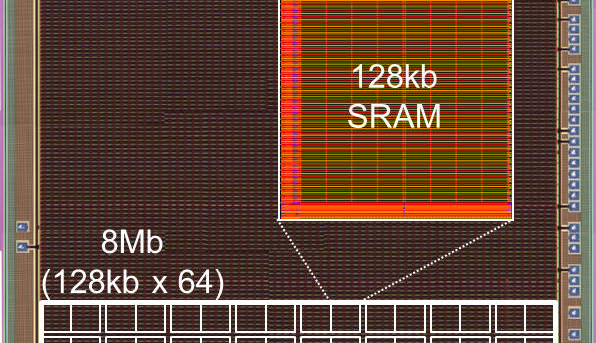

13,7 nW/Mbit ist die neue Rekordmarke, die Renesas bei einem embedded Low-Power-SRAMs erreicht hat. Dabei konnte die Geschwindigkeit von 1,8 ns für aktives Auslesen gehalten werden. Laut Renesas wurde der SRAM-Prototyp in 65-nm-Technologie im SOTB-Prozess (Silicon On Thin Buried oxide) gefertigt. Der Verbrauch wird durch eine Vorspannung des Substrats erreicht, um einen guten Kompromiss zwischen Geschwindigkeit und Leckströmen zu erreichen. Mit dieser Technik konnten typische Probleme konventioneller CMOS-Strukturen wie erhöhter Leckstrom bei niedrigen Gate-Schwellspannungen und eine erhöhte Variabilität der Gate-Schwellspannungen erreicht werden.

Die wichtigste Varianzquelle der Schwellspannungen bei konventionellen kleinen Transistoren ist, dass so wenige Dotierungs-Atome im Kanal vorhanden sind und somit nur wenige Atome mehr oder weniger die Schwellspannungen deutlich beeinflussen. Mit STOB, und anderen FDSoI-Prozessen (Fully-Depleted Silicon-on-Insulator) variieren keine Atomzahlen im Kanal.

Der normale im Vergleich zum High-Speed-Mode (keine Substrat-Vorspannung versus adäquate Vorspannung) ändert die Auslesezeiten von 4,58 auf nur 1,84 ns. Eine umgekehrte Vorspannung hingegen reduziert die Leckströme um den Faktor 1000 im Vergleich zum normalen Modus. Auf diese Weise wurde dann der Rekord von nur 13,7 nW/Mbit erzielt.

Die Forschungsergebnisse, die zu diesem Prototypen führten, wurden am 8. Juni auf dem VLSI-Symposium in Kyoto vorgestellt. Renesas geht davon aus, dass sich diese SM-Technik gut als Ersatz für nicht flüchtigen Speicher bei Anwendungen rund um Energy-Harvesting oder bei Batteriebetrieb im Bereich IoT, Heimelektronik und in der Medizinelektronik einsetzen lässt.

Die wichtigste Varianzquelle der Schwellspannungen bei konventionellen kleinen Transistoren ist, dass so wenige Dotierungs-Atome im Kanal vorhanden sind und somit nur wenige Atome mehr oder weniger die Schwellspannungen deutlich beeinflussen. Mit STOB, und anderen FDSoI-Prozessen (Fully-Depleted Silicon-on-Insulator) variieren keine Atomzahlen im Kanal.

Der normale im Vergleich zum High-Speed-Mode (keine Substrat-Vorspannung versus adäquate Vorspannung) ändert die Auslesezeiten von 4,58 auf nur 1,84 ns. Eine umgekehrte Vorspannung hingegen reduziert die Leckströme um den Faktor 1000 im Vergleich zum normalen Modus. Auf diese Weise wurde dann der Rekord von nur 13,7 nW/Mbit erzielt.

Die Forschungsergebnisse, die zu diesem Prototypen führten, wurden am 8. Juni auf dem VLSI-Symposium in Kyoto vorgestellt. Renesas geht davon aus, dass sich diese SM-Technik gut als Ersatz für nicht flüchtigen Speicher bei Anwendungen rund um Energy-Harvesting oder bei Batteriebetrieb im Bereich IoT, Heimelektronik und in der Medizinelektronik einsetzen lässt.

Mehr anzeigen

Weniger anzeigen

Diskussion (0 Kommentare)