Wolkenkratzer-Architektur macht Chips tausendmal besser

21. Dezember 2015

über

über

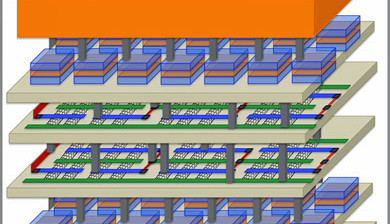

Forscher der Stanford University haben eine neue Chip-Architektur entwickelt, die die Leistungen eines Chips um den Faktor 1000 im Vergleich zu konventionellen Chips erhöhen soll. Die Chips im Wolkenkratzerformat sind aus Lagen von Kohlenstoff-Nanoröhren-Transistoren und resistiven RAM-Zellen aufgebaut.

Die Wissenschaftler nennen ihre neue Architektur „Nano-Engineered Computing Systems Technology“ (N3XT). Dabei werden Prozessoren und Speicherzellen wie die Etagen eines Wolkenkratzers aufeinandergestapelt und durch tausende von Vias miteinander verbunden. Dadurch können Daten schneller und energiesparender zwischen den „Stockwerken“ transportiert werden.

Silizium ist als Basismaterial für die neuen Chips nicht geeignet, da bei der Produktion von Siliziumchips hohe Temperaturen erforderlich sind. Die hohen Temperaturen würden beim Aufbringen einer neuen Lage die darunter liegenden Lagen beschädigen. Deshalb verwendet man bei den Wolkenkratzer-Chips Kohlenstoff-Nanoröhrchen-Transistoren (CNTs) und resistive RAM-Zellen, die sich bei niedrigeren Temperaturen produzieren lassen.

Die Forscher haben auch mit magnetischen Nanomaterialien zur Speicherung von Daten experimentiert. Damit die Wärme, die durch die unteren Lagen produziert wird, nicht die Arbeit in den darüber liegenden Etagen stört, haben die Forscher „Mezzanine“ mit Kühleigenschaften zwischen die einzelnen Lagen geschaltet. Im letzten Jahr konnten die Wissenschaftler schon ein funktionsfähiges Exemplar mit je zwei Lagen CNTs und RRAM präsentieren.

Die Ergebnisse der Untersuchung wurden vor kurzem publiziert in Rebooting Computing, einer Sonderausgabe der Zeitschrift IEEE Computer.

Die Wissenschaftler nennen ihre neue Architektur „Nano-Engineered Computing Systems Technology“ (N3XT). Dabei werden Prozessoren und Speicherzellen wie die Etagen eines Wolkenkratzers aufeinandergestapelt und durch tausende von Vias miteinander verbunden. Dadurch können Daten schneller und energiesparender zwischen den „Stockwerken“ transportiert werden.

Silizium ist als Basismaterial für die neuen Chips nicht geeignet, da bei der Produktion von Siliziumchips hohe Temperaturen erforderlich sind. Die hohen Temperaturen würden beim Aufbringen einer neuen Lage die darunter liegenden Lagen beschädigen. Deshalb verwendet man bei den Wolkenkratzer-Chips Kohlenstoff-Nanoröhrchen-Transistoren (CNTs) und resistive RAM-Zellen, die sich bei niedrigeren Temperaturen produzieren lassen.

Die Forscher haben auch mit magnetischen Nanomaterialien zur Speicherung von Daten experimentiert. Damit die Wärme, die durch die unteren Lagen produziert wird, nicht die Arbeit in den darüber liegenden Etagen stört, haben die Forscher „Mezzanine“ mit Kühleigenschaften zwischen die einzelnen Lagen geschaltet. Im letzten Jahr konnten die Wissenschaftler schon ein funktionsfähiges Exemplar mit je zwei Lagen CNTs und RRAM präsentieren.

Die Ergebnisse der Untersuchung wurden vor kurzem publiziert in Rebooting Computing, einer Sonderausgabe der Zeitschrift IEEE Computer.

Mehr anzeigen

Weniger anzeigen

Diskussion (0 Kommentare)