Surrounding Gate für 5 nm SRAM

über

Miniaturisierung ist das A & O in der Halbleitertechnik. Der weiteren Gültigkeit von Moore's Law steht aber entgegen, dass sich die Strukturen unaufhaltsam der Größe einzelner Atome annähern. Eine vertikale Surrounding-Gate-Technik von Unisantis erlaubt es nun, eine SRAM-Zelle aus sechs Transistoren auf eine unglaublich kleine Fläche von 0,0184 bis 0,0205 μm² zu komprimieren. Eine auf solchen SGTs basierende Zelle benötigt eine um 20 bis 30 % reduzierte Fläche im Vergleich zu horizontalen SGTs. Außerdem ergeben sich Vorteile bei der Betriebsspannung und der Stabilität.

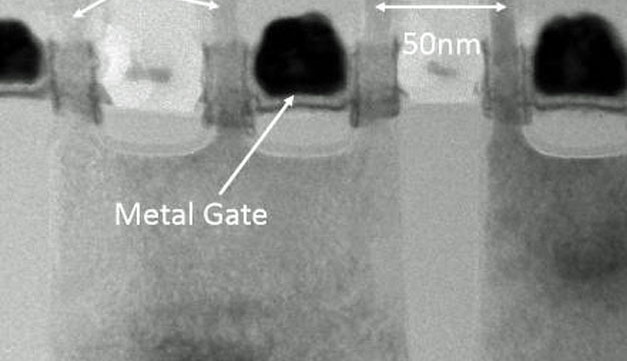

Mit den vertikalen Surroundig Gates ergibt sich eine nahezu perfekte Steuerung des Kanals des FETs. Eine damit aufgebaute SRAM-Zelle erlaubt eine Fläche von nur 0,0205 μm² bei einer minimalen Pillar Pitch von 50 nm, was zu einer um 24 % besseren Flächenausnutzung im Vergleich zu den kleinsten konventionellen SRAM-Zellen führt. Die Fertigungskosten sollen dabei vergleichbar zu konventionellen finFET-basierten SRAMs sein, wenn die Anzahl der Prozessschritte durch EUV-Lithografie gering gehalten wird.

Diskussion (0 Kommentare)