SSD-Flash mit 112 Layern

3. Februar 2020

über

über

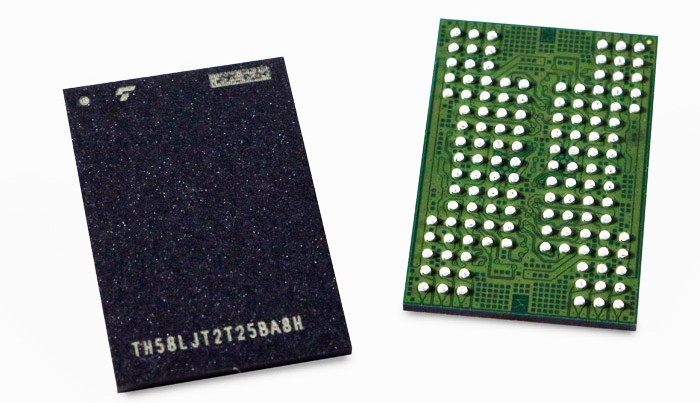

Der Halbleiter-Hersteller Kioxia, hervorgegangen aus einer Umbenennung der früheren Toshiba Memory Corporation und seinem Partner Western Digital, haben beim 3D-Flash BiCS als Flash-Speicher der fünften Generation einen vertikalen Flash-Stapel aus 112 Layern realisiert.

Mit der BiCS5-Technologie lassen sich Speicher mit TLC- und QLC-Zellen für SSDs fertigen. Das Verfahren bietet viel Kapazität, Leistung und Zuverlässigkeit zu günstigen Preisen. Kioxia plant, ihre Kunden In Q1 2020 mit Mustern zu beliefern. TLC-Chips weisen dann eine Kapazität von 512 Gb = 64 GB auf. Der Einsatz von BiCS5 in der Massenfertigung soll ab Q3 2020 stattfinden. Die neuen Flash-Chips werden dann in vielen Mobilgeräten und Computern zu finden sein. Geplant ist auch der Ausbau der Prozesstechnologie in Richtung noch größerer Kapazitäten wie etwa TLC-Chips mit 128 GB oder QLC-Chips mit 166 GB.

Weitere Verfahren erhöhen die Zell-Dichte auch horizontal erheblich. Die Fortschritte bei der lateralen Skalierung kombiniert mit 112 vertikalen Layern ermöglicht im Vergleich zur Vorläufertechnologie mit 96 Layern eine Kapazitätssteigerung um bis zu 40 % bei reduzierten Kosten. Die BiCS5-Technologie bringt dabei auch eine Steigerung der I/O-Leistung um bis zu 50 % mit sich. Flash-Chips im BiCS-Verfahren wird Kioxia in seinem Werk in Yokkaichi und Kitakami fertigen.

Mit der BiCS5-Technologie lassen sich Speicher mit TLC- und QLC-Zellen für SSDs fertigen. Das Verfahren bietet viel Kapazität, Leistung und Zuverlässigkeit zu günstigen Preisen. Kioxia plant, ihre Kunden In Q1 2020 mit Mustern zu beliefern. TLC-Chips weisen dann eine Kapazität von 512 Gb = 64 GB auf. Der Einsatz von BiCS5 in der Massenfertigung soll ab Q3 2020 stattfinden. Die neuen Flash-Chips werden dann in vielen Mobilgeräten und Computern zu finden sein. Geplant ist auch der Ausbau der Prozesstechnologie in Richtung noch größerer Kapazitäten wie etwa TLC-Chips mit 128 GB oder QLC-Chips mit 166 GB.

Weitere Verfahren erhöhen die Zell-Dichte auch horizontal erheblich. Die Fortschritte bei der lateralen Skalierung kombiniert mit 112 vertikalen Layern ermöglicht im Vergleich zur Vorläufertechnologie mit 96 Layern eine Kapazitätssteigerung um bis zu 40 % bei reduzierten Kosten. Die BiCS5-Technologie bringt dabei auch eine Steigerung der I/O-Leistung um bis zu 50 % mit sich. Flash-Chips im BiCS-Verfahren wird Kioxia in seinem Werk in Yokkaichi und Kitakami fertigen.

Mehr anzeigen

Weniger anzeigen

Diskussion (0 Kommentare)