Dritte Dimension als Umgehung von Moore's Law

über

Die Forscher meinen, dass dieses Verfahren außerdem die Notwendigkeit eines zweiten Chips zur Wandlung zwischen Hoch- (Peripherie) und Niederspannungssignalen (Cores) überflüssig macht.

Moore's Law

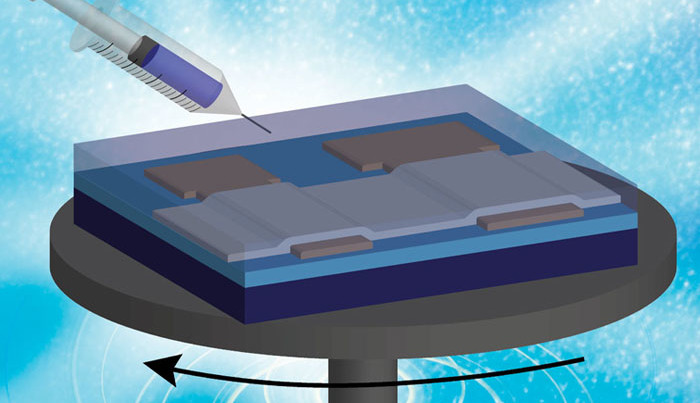

Moore's Law besagt, dass sich die Transistorendichte etwa alle zwei Jahre verdoppelt. Da Siliziumtransistoren so immer kleiner wurden, sind auch deren Betriebsspannungen niedriger geworden. Höhere Spannungen aber würden die winzigen Transistoren beschädigen. Daher sind die internen Strukturen moderner CPUs nicht direkt mit den Pegeln der Peripherie kompatibel. Mit Hilfe von 3D-Anordnungen ist aber die Integration von Transistoren für unterschiedliche Pegel möglich, denn die zweite Schicht von Transistoren kann mit höheren Spannungen umgehen und ermöglicht so einen kompakteren Chip.Die Forscher verwendeten für die zweite Schicht mit amorphem Metalloxid eine andere Art Halbleiter. Um die untere Schicht aus Silizium nicht zu beschädigen, wurde sie mit einer Lösung benetzt, die Zink und Zinn enthält. Per Fliehkraft wurde eine gleichmäßige Abdeckschicht generiert. Dann wurde der Chip getrocknet.

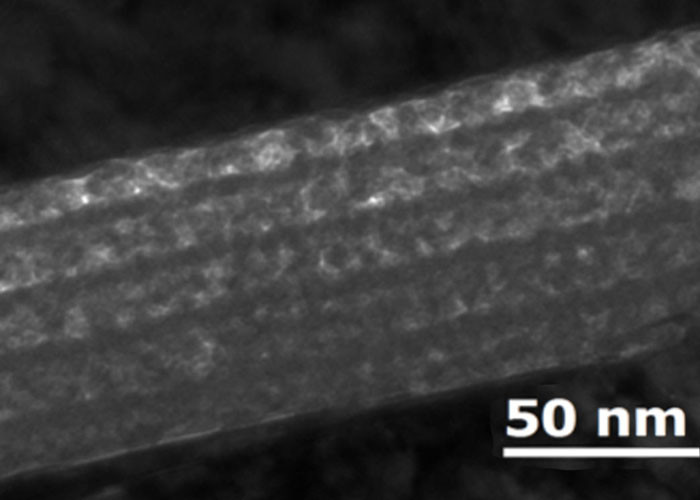

Dies wurde so oft wiederholt, bis die Zink-Zinn-Schicht eine Stärke von etwa 75 nm erreicht hatte. Während eines letzten Trocknens reagierten die Metalle mit dem Luft-Sauerstoff, und das Resultat war eine Schicht aus Zink-Zinn-Oxid. Aus dieser Schicht wurden Dünnschichttransistoren gefertigt, die höhere Spannungen vertragen als das darunterliegende Silizium.

Bild: Youngbae Son und Rose Anderson, Peterson Lab / UM.

Nun mussten die beiden Schichten noch verbunden werden. Hierfür wurden vertikale Dünnfilm-Dioden und Schottky-Transistoren in der Zink-Zinn-Oxid-Schicht realisiert. Diese Bauteile dienen zur Pegelanpassung der beiden Schichten. Dieses Verfahren ebnet den Weg zu ICs, die höher integriert sind, als es Moore’s Law erlaubt.

Diskussion (0 Kommentare)