Auswirkungen des DDR5-Transmitter-Tests

über

DDR5 verwendet einen expliziten Fullrate Clock. Das Taktsignal steuert das Befehlssignal und das Strobe-Signal taktet die Daten. Der Bus ist breit und single ended. Eine Server-Blade kann über tausend parallele Datenkanäle enthalten. Die Lese- und Schreibbefehle sind bidirektional. Das bedeutet, dass sich Lese- und Schreibdaten überschneiden. Im Gegensatz zu anderen seriellen Bussignalen können das Strobe-Signal und die Daten durch eingefügte Ruhephasen in unterbrochener Weise übertragen werden (idle states). DDR5 wird im Vergleich zu DDR4 mit einer mindestens doppelt so hohen Geschwindigkeit arbeiten (2133 MT/s bei DDR1, DDR2 und DDR3). Es gibt bei DDR5 daher mehrere Signal-Eigenschaften, die anders als bei DDR4 getestet und verifiziert werden müssen.

Hypergeschwindigkeit

Die Signale verwenden Hochgeschwindigkeits-Übertragungsleitungen, bei denen Timing und Impedanz problematisch werden. Bereits bei DDR4-Technologie hat sich der große Wandel vollzogen. DDR4 arbeitet mit bis zu 4200 MT/s und gilt als schneller serieller Bus. Die Bewertung des Data Valid Window mit seinen Augendiagrammen und Empfängermasken ist eine wichtige Aufgabe für den Entwickler. Jetzt, da DDR5 mit der Hypergeschwindigkeit von 6400 MT/s arbeitet, lautet die Frage: Kann im Augendiagramm noch ein offenes Auge erreicht werden? Wenn ja, gelten die für die Entwicklungsphasen von DDR4 verwendeten Tests auch noch für DDR5? Wenn nicht, müssen wir eventuell andere Techniken wie zum Beispiel Equalizer verwenden, um die geforderten Ziele zu erreichen.Die Signalintegrität ist ein großes Problem bei der Charakterisierung von DDR5 DRAM-Transmittern. Die größte Herausforderung beim Testen einer DDR5-Anwendung ist die Trennung von Lese- und Schreibdaten. Alte Methoden, wie die Verwendung von Strobe- und Datensignalen oder die Identifizierung des Lese- und Schreib-Vorverstärkungsmusters sind möglicherweise nicht mehr anwendbar. Da die Signalintegrität eine große Herausforderung darstellen wird, können neben den bisherigen elektrischen Tests sowie neben den Timing- und Augendiagrammtests auch neue Testparameter erforderlich sein. Auch Jitter kann nun zu einem wichtigen Charakterisierungsmerkmal werden. Schnellere Datenraten, vor allem bei Geschwindigkeiten über 3600 MT/s, können dazu führen, dass sich die Augendiagramme schließen.

Jede Kleinigkeit zählt also. Bei der Auswahl der Prüfgeräte sollte besonders auf die Rausch- und Jitterleistung geachtet werden. Neue Methoden zur Charakterisierung der Daten werden auch benötigt, wenn kein Augendiagramm vorliegt. Es kann sein, dass eine Ausgleichsmethode, wie z.B. die Decision Feedback Equalization, erforderlich ist, um das Auge innerhalb einer Augendiagramm-Messung zu öffnen.

Zugriff auf die Signale

Vor den Charakterisierungen müssen wir uns jedoch zunächst Zugang zu den interessanten Signalen wie Taktgeber, Strobe, Daten und Befehlen verschaffen. Via-Zugriffe stellen die beste Möglichkeit dazu dar, da man direkt am DRAM sondieren kann. Der Via-Zugriff ist jedoch begrenzt, vor allem wenn die Boards mit mehreren verschiedenen Geräten mit möglichst wenig Keep-Out-Volume bestückt werden.Die nächste Option wäre die Verwendung eines BGA-Interposers. Dieser sortiert alle interessanten Signale zum Testen aus. Er wird über eine BGA-Rework Station auf die Platine gelötet und das DRAM wird dann ebenfalls damit wiederum auf den Interposer gelötet. Für die Verbindung zum Oszilloskop werden ZIF- oder Mikrotastköpfe verwendet. Es ist sehr wichtig, den Bus nicht zu unterbrechen, wenn Sie den Interposer laden.

Augendiagramm-Untersuchungen

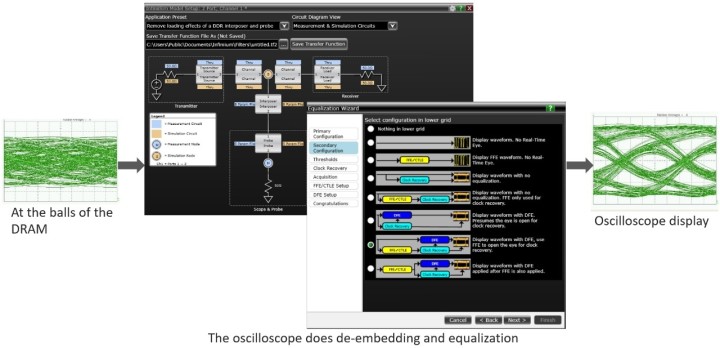

Der Entwickler muss sicherstellen, dass der Interposer die Geschwindigkeit des Signals mit minimaler Belastung bewältigt. Selbst wenn er den Bus nicht unterbricht, müssten Sie wahrscheinlich ein De-Embedding der Signale vornehmen. Verwenden Sie die S‑Parameter‑Dateien in der De-Embedding-Software, um eine Übertragungsfunktions-Datei zu erstellen, die den Frequenzgang des Signals korrigiert. Bei höheren Datenraten (über 3000 MT/s) wird ein Zusammenbruch des Auges im Augendiagramm am DRAM aufgrund von Intersymbolstörungen erwartet. DDR5 wird unter anderem wahrscheinlich eine Entzerrung der Decision Feedback Equalization erforderlich machen, um das Augendiagramm der Daten zu verbessern, nachdem es vom Empfänger aufgenommen wurde. Das verwendete Ausgleichsverfahren muss in der Lage sein, das Auge zu öffnen, ohne das reflexionsbedingte Rauschen zu verstärken (Bild 1).

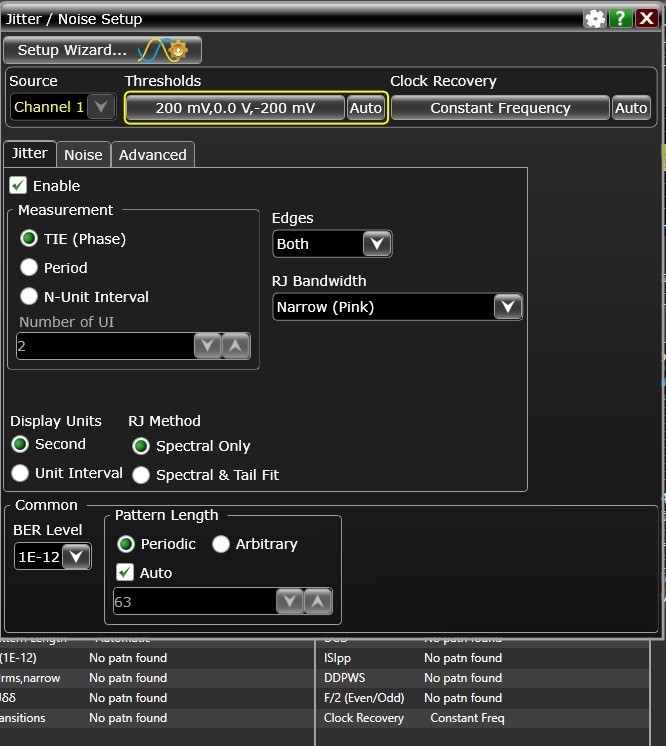

Es handelt sich hier um einen der kritischeren DRAM-Compliance-Tests, der auch für DDR5 von entscheidender Bedeutung sein wird. Für die Jitter-Charakterisierung ist es wichtig, zufällige und deterministische Jitterkomponenten trennen zu können (Bild 2). Dadurch kann der Entwickler die Ursache für potenzielle Rausch-, Übersprech- oder Tastverzerrungen identifizieren.

von zufälligem und deterministischem Jitter.

Ein Augendiagrammtest führt Messungen von Höhe und Breite des Auges in einem Augendiagramm durch. Wenn das Auge geschlossen ist, muss eine Ausgleichsmethode verwendet werden, um es zu öffnen. Die Messungen der Augenbreite und -höhe müssen das Rauschen des Instruments berücksichtigen. Dies gilt auch für Jittermessungen.

Die Komplexität von DDR5 erfordert Simulationen, Analysen, Debugging und Compliance-Tests während der Entwicklung. Der betreffende Workflow muss für eine Datenanalyse sorgen, die Messkorrelationen zwischen Simulation, Versuchsplanung und Konformität durchführen kann. Moderne Simulationswerkzeuge ermöglichen die Ausgabe von Wellenformdateien, die in der Compliance-Testsoftware für einen frühen Test verwendet werden können, bevor ein reales Gerät zum Testen verfügbar ist.

Wenn einer der Tests fehlschlägt, kann mit Hilfe eines Datenanalysetools ein frühzeitiges Redesign oder eine Optimierung durchgeführt werden, um den Optimierungspunkt zu finden. Wenn dann ein tatsächlicher Prüfling zur Verfügung steht, kann eine Messkorrelation durchgeführt werden, um die Leistung und die Marge innerhalb der Entwicklung weiter zu verfeinern.

Fazit

Das erfolgreiche Testen von DDR5-Transmittern hängt davon ab, welche Werkzeuge Sie zur Durchführung der Messungen verwenden. Ein komplettes DDR5-Transmitter-Mess-System besteht aus einer Sonde, einem Oszilloskop und einer Konformitäts- oder Validierungssoftware, die alle Testgeschwindigkeiten und -Parameter abdeckt.Das verwendete Oszilloskop muss möglichst geringe Jitter- und Rauschleistungen aufweisen. Zudem muss ein automatisiertes Softwarepaket für Compliance- oder Validierungsarbeiten verwendet werden, um Interoperabilität und Wiederholbarkeit sicherzustellen. Sie können die Messungen manuell mit einem Oszilloskop durchführen, aber die Übersetzung der Prüfparameter in einzelne Mess-Schritte kann langwierig sein und mehr Prüfzeit in Anspruch nehmen.

Die Autorin

Die Autorin

Ailee Grumbine ist auf Datenanalyse und Hochgeschwindigkeits-Speichertechnologien wie DDR- und SD-UHS-Schnittstellen spezialisiert. Sie schloss ihr Studium an der University of Science Malaysia im Jahre 2001 ab und erwarb den Titel einen Master of Business Administration an der University of Colorado in Colorado Springs. Vor ihrer jetzigen Position war Ailee eine regionale Anwendungsingenieurin mit Spezialkenntnissen in Hochgeschwindigkeitsbus-Anwendungen, die Tests physikalischer DDR-Speicherebenen und Protokolltests umfassen.(190239)

➔ Wollen Sie weitere ElektorLabs-Artikel lesen? Jetzt Elektor-Mitglied werden!

Diskussion (0 Kommentare)