VLSI Symposien: Samsung mit EUV für Massenherstellung von 7-nm-Chips

2. Juli 2018

über

über

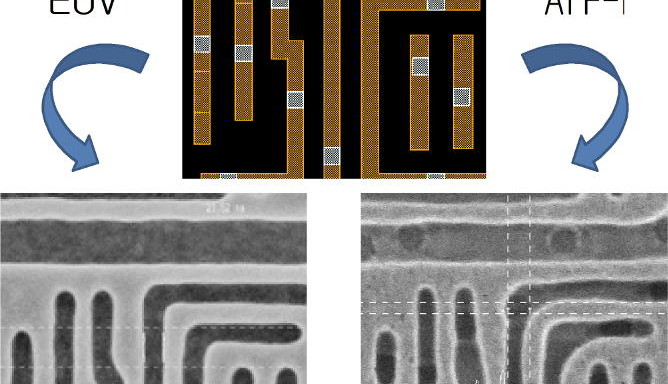

Auf der VLSI 2018 stellte Samsung seine kommende 7-nm-FinFET-Technologie vor, die als erste Halbleiterherstellungstechnologie mit EUV-Lithografie eingesetzt wird – EUV soll bessere Gleichmäßigkeit und Kostenvorteile gegenüber Standard-Multi-Patterning-Ansätzen für extreme Skalierung bieten.

Samsung verwendet EUV mit zusätzlicher Front-End-Skalierung, speziellen Konstruktionen und einer einziger Diffusionsschicht, um Transistoren mit einem Fin-Pitch von 27 bzw. 54 nm zu realisieren, was eine Reduzierung des Leistungsbedarfs um 50 bis 60 % gegenüber der bisher verwendeten 10-nm-Technologie ergab.

Samsung produzierte ein 256-Mbit-SRAM-Array mit einer Zellengröße von nur 0,0262 µm² zusammen mit CPU/GPU-Logikschaltungen, die alle die NBTI-Zuverlässigkeitsanforderungen erfüllten.

Unabhängig davon wurde eine 8-n-FinFET-Logiktechnologie für mobile, leistungsstarke und stromsparende Anwendungen entwickelt. Der neue 8LPP-Prozess ist eine Erweiterung des bestehenden 10-nm-Prozesses der Serienproduktion. 8LPP verbraucht 7 % weniger Strom, ist rund 15 % kleiner und kann mit nur 0,35 V betrieben werden. Diese Verbesserungen sind auf die kontinuierliche Skalierung sowie auf reduzierten Übergangswiderstand und ein besseres Leckageprofil zurückzuführen.

Samsung verwendet EUV mit zusätzlicher Front-End-Skalierung, speziellen Konstruktionen und einer einziger Diffusionsschicht, um Transistoren mit einem Fin-Pitch von 27 bzw. 54 nm zu realisieren, was eine Reduzierung des Leistungsbedarfs um 50 bis 60 % gegenüber der bisher verwendeten 10-nm-Technologie ergab.

Samsung produzierte ein 256-Mbit-SRAM-Array mit einer Zellengröße von nur 0,0262 µm² zusammen mit CPU/GPU-Logikschaltungen, die alle die NBTI-Zuverlässigkeitsanforderungen erfüllten.

Unabhängig davon wurde eine 8-n-FinFET-Logiktechnologie für mobile, leistungsstarke und stromsparende Anwendungen entwickelt. Der neue 8LPP-Prozess ist eine Erweiterung des bestehenden 10-nm-Prozesses der Serienproduktion. 8LPP verbraucht 7 % weniger Strom, ist rund 15 % kleiner und kann mit nur 0,35 V betrieben werden. Diese Verbesserungen sind auf die kontinuierliche Skalierung sowie auf reduzierten Übergangswiderstand und ein besseres Leckageprofil zurückzuführen.

Mehr anzeigen

Weniger anzeigen

Diskussion (0 Kommentare)