Konfigurierbarer Analogchip viel sparsamer als die digitale Version

16. März 2016

über

über

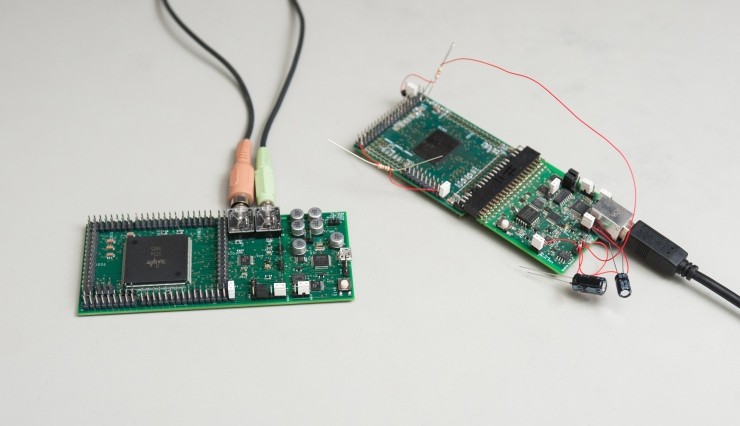

Wissenschaftler des Georia Institute of Technology in Atlanta (USA) haben einen konfigurierbaren Rechenchip entwickelt, der viel weniger Energie benötigt als ein vergleichbarer digitaler Chip und dessen Abmessungen zudem noch bedeutend geringer sind.

Das neue IC wurde Field-Programmable Analog Array (FPAA) System-On-Chip (SoC) getauft und verbindet analoge Technologie mit digitalen Komponenten, die diesen geringen Energiehunger und diese geringen Abmessungen ermöglichen. Die Leistungsaufnahme analoger Arrays liegt bei einigen Milliwatt, während ein FPGA locker ein Watt zum Betrieb benötigt. Der FPAA ist nicht-flüchtig, genau wie ein Flash-Speicher. Professionellen Entwicklern, die sich gut mit FPGAs auskennen, wird schnell die starke Ähnlichkeit der Programmierinterfaces digitaler und analoger Arrays auffallen.

Laut den Forschern sind die neuen „analogen“ Low-power-Chips in viele Anwendungen genauso gut einsetzbar wie konventionelle konfigurierbare digitale Arrays (FPGAs).

Das neue IC wurde Field-Programmable Analog Array (FPAA) System-On-Chip (SoC) getauft und verbindet analoge Technologie mit digitalen Komponenten, die diesen geringen Energiehunger und diese geringen Abmessungen ermöglichen. Die Leistungsaufnahme analoger Arrays liegt bei einigen Milliwatt, während ein FPGA locker ein Watt zum Betrieb benötigt. Der FPAA ist nicht-flüchtig, genau wie ein Flash-Speicher. Professionellen Entwicklern, die sich gut mit FPGAs auskennen, wird schnell die starke Ähnlichkeit der Programmierinterfaces digitaler und analoger Arrays auffallen.

Laut den Forschern sind die neuen „analogen“ Low-power-Chips in viele Anwendungen genauso gut einsetzbar wie konventionelle konfigurierbare digitale Arrays (FPGAs).

Mehr anzeigen

Weniger anzeigen

Diskussion (0 Kommentare)