embOS/IP: Mehrere virtuelle Ethernet-Ports an Single Port MCUs einrichten

4. Februar 2016

über

über

Der TCP/IP-Stack von SEGGER unterstützt ab sofort das Tail Tagging-Feature von Micrel/Microchip Ethernet Switches. embOS/IP ist der erste IP-Stack im embedded Bereich, der dieses Feature unterstützt.

Damit ist es möglich, auf einer CPU mehrere virtuelle Ethernet-Ports anzubieten, obwohl nur ein Port physisch vorhanden ist. Dies funktioniert dank der Wahl eines anderen PHY.

Die Einrichtung eines weiteren Ethernet-Ports kann sehr komplex und aufwändig sein, da die meisten CPUs nur über einen Ethernet-Controller verfügen. Zusätzliche Hardware-Komponenten wie externe Ethernet-Controller sind in solchen Fällen notwendig, um die Zahl der verfügbaren Ports zu erhöhen. Micrel/Microchip hat Switches entwickelt, die mit Hilfe des so genannten Tail Tagging-Modus aus einem Ethernet-Port 1+n einzeln ansteuerbare Ports machen können.

Mehrere Ports sind beispielsweise notwendig beim Bau eines Routers, bei dem jeder Port individuell ansprechbar sein muss. Auch beim Aufbau redundanter Netzwerke - bekannt als Multihoming - können mehrere Ports erforderlich sein.

Die Adressierung der Ports erfolgt rein auf Software-Basis und ist transparent für Dritte. Das neue Feature erlaubt es jedem der Ports, eine eigene MAC-Adresse zu haben, so dass sie in einem Netzwerk wie unterschiedliche physische Hosts erscheinen. Zusätzlich bietet SEGGER auch Hardware für die Evaluierung des neuen Features an.

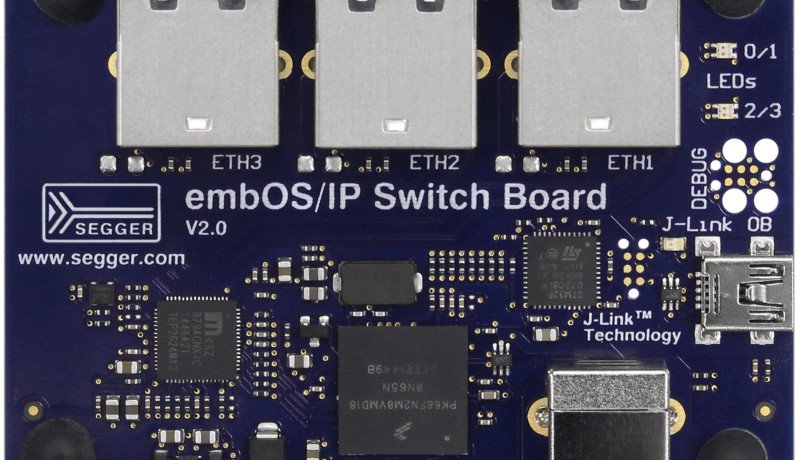

Das embOS/IP Switch Board verfügt über eine NXP Kinetis K66 CPU, den Micrel/Microchip Switch PHY KSZ8794CNX mit drei Ethernet-Ports und einer On-board Version der marktführenden Debug Probe J-Link von SEGGER. Tail Tagging ist zusammen mit einem PHY-Treiber als Add-on für embOS/IP erhältlich. Das Paket kann auch mit der Entwicklungsumgebung SEGGER Embedded Studio im Eval-Modus einfach getestet werden.

Weitere Informationen zu Tail Tagging finden sich unter https://www.segger.com/embos-ip-tail-tagging.html.

Details zum embOS/IP Switch Board sind hier verfügbar: https://www.segger.com/embos-ip-switch-board.html

Damit ist es möglich, auf einer CPU mehrere virtuelle Ethernet-Ports anzubieten, obwohl nur ein Port physisch vorhanden ist. Dies funktioniert dank der Wahl eines anderen PHY.

Die Einrichtung eines weiteren Ethernet-Ports kann sehr komplex und aufwändig sein, da die meisten CPUs nur über einen Ethernet-Controller verfügen. Zusätzliche Hardware-Komponenten wie externe Ethernet-Controller sind in solchen Fällen notwendig, um die Zahl der verfügbaren Ports zu erhöhen. Micrel/Microchip hat Switches entwickelt, die mit Hilfe des so genannten Tail Tagging-Modus aus einem Ethernet-Port 1+n einzeln ansteuerbare Ports machen können.

Mehrere Ports sind beispielsweise notwendig beim Bau eines Routers, bei dem jeder Port individuell ansprechbar sein muss. Auch beim Aufbau redundanter Netzwerke - bekannt als Multihoming - können mehrere Ports erforderlich sein.

Die Adressierung der Ports erfolgt rein auf Software-Basis und ist transparent für Dritte. Das neue Feature erlaubt es jedem der Ports, eine eigene MAC-Adresse zu haben, so dass sie in einem Netzwerk wie unterschiedliche physische Hosts erscheinen. Zusätzlich bietet SEGGER auch Hardware für die Evaluierung des neuen Features an.

Das embOS/IP Switch Board verfügt über eine NXP Kinetis K66 CPU, den Micrel/Microchip Switch PHY KSZ8794CNX mit drei Ethernet-Ports und einer On-board Version der marktführenden Debug Probe J-Link von SEGGER. Tail Tagging ist zusammen mit einem PHY-Treiber als Add-on für embOS/IP erhältlich. Das Paket kann auch mit der Entwicklungsumgebung SEGGER Embedded Studio im Eval-Modus einfach getestet werden.

Weitere Informationen zu Tail Tagging finden sich unter https://www.segger.com/embos-ip-tail-tagging.html.

Details zum embOS/IP Switch Board sind hier verfügbar: https://www.segger.com/embos-ip-switch-board.html

Mehr anzeigen

Weniger anzeigen

Diskussion (0 Kommentare)